這也引起行業對于AMD第二代EYPC處理器的極大關注。自去年11月AMD首次公布代號為“Rome”的第二代EYPC處理器的一些特性,包括采用7nm制程工藝,最高64個Zen2核心、支持PCIe4.0等之后,在今年的臺北電腦展上,AMD首席執行官Dr.LisaSu終于明確表示第二代EPYC服務器處理器會于第三季度推出。

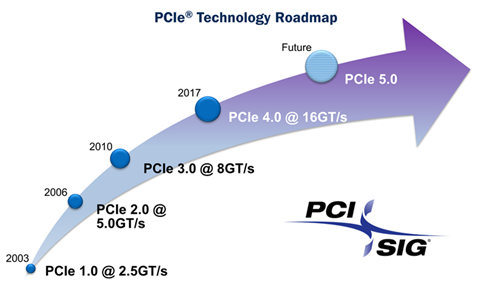

通道帶寬翻倍PCIe4.0為數據中心賦能

除了制程工藝上的領先,AMD第二代EPYC的一大亮點是行業首款支持PCIe4.0規范的x86服務器處理器。目前業界使用的普遍是PCIe3.0標準,雖然帶寬達到了8GT/s,但其實這已經是9年前制定的標準。2017年發布的PCIe4.0標準進一步提升了帶寬,達到16GT/s,然而在今年6月之前的近兩年間市面上并沒有支持的產品上市。AMD的第三代銳龍處理器與X570主板成為首款,而同樣采用Zen2核心的第二代EYPC處理器也支持這一先進特性。

相比PCIe3.0,PCIe4.0讓每通道帶寬實現翻倍,尤其是對AMDInifityFabric互連總線來說可以徹底消除瓶頸,無論是雙路霄龍之間互連,還是對外連接擴展卡都更加游刃有余。再加上多達128條Lanes的支持,可大幅度提升新一代高性能顯卡、聯網設備、NVMe存儲、局域網卡等設備的性能帶寬,尤其是對存儲設備帶來的性能提升,將會是質的飛躍。

對于有高速數據處理需求的數據中心、高性能計算、云計算等領域來說,超高帶寬的PCIe4.0通道帶來的性能提升是非??捎^的,可以進一步為數據中心加速。

神秘面紗即將揭開AMDYes唱響全場

到今天為止,Rome的面容仍然隱藏在幕后,但僅僅從目前透露的信息來看,已經讓很多從業者興奮不已:8個CPU核心單元每個有8個CPU內核總計8×8=64個核心128線程;I/O單元與核心分離,整合了DDR控制器、PCIe4.0/3.0總線和InfinityFabric等I/O等功能;將這種全新的設計方法與7nm制程技術結合,通過重新優化的指令緩存和更大的運行緩存,更強的浮點性能,將真正實現性能、功耗和良品率的出色平衡。

隨著第三季度的臨近,AMD第二代EYPC處理器也將呼之欲出。攜先進的7nm制程工藝、64核心、PCIe4.0等一系列創新領先特性,Rome將真正為數據中心提升性能、減少能耗,并帶來顯著的TCO降低。“AMDYes”的呼聲也將在服務器市場唱響!